- 您现在的位置:买卖IC网 > Sheet目录311 > AS5140 PB (ams)BOARD PROGRAM AS5140

�� �

�

�

�AS5140H�

�Data� Sheet� -� D� e� t� a� i� l� e� d� D� e� s� c� r� i� p� t� i� o� n�

�Programming� Daisy� Chained� Devices.� In� Daisy� Chain� mode,� the� Prog� pin� is� connected� directly� to� the� DO� pin� of� the� subsequent� device� in�

�the� chain� (see� Figure� 6)� .� During� programming� (see� Programming� the� AS5140H� on� page� 19)� ,� a� programming� voltage� of� 7.5V� must� be� applied� to�

�pin� Prog.� This� voltage� level� exceeds� the� limits� for� pin� DO,� so� one� of� the� following� precautions� must� be� made� during� programming:�

�Open� the� connection� DO� →� Prog� during� programming,� (or)�

�Add� a� Schottky� diode� between� DO� and� Prog� (Anode� =� DO,� Cathode� =� Prog)�

�Due� to� the� parallel� connection� of� CLK� and� CSn,� all� connected� devices� may� be� programmed� simultaneously.�

�7.2� Incremental� Outputs�

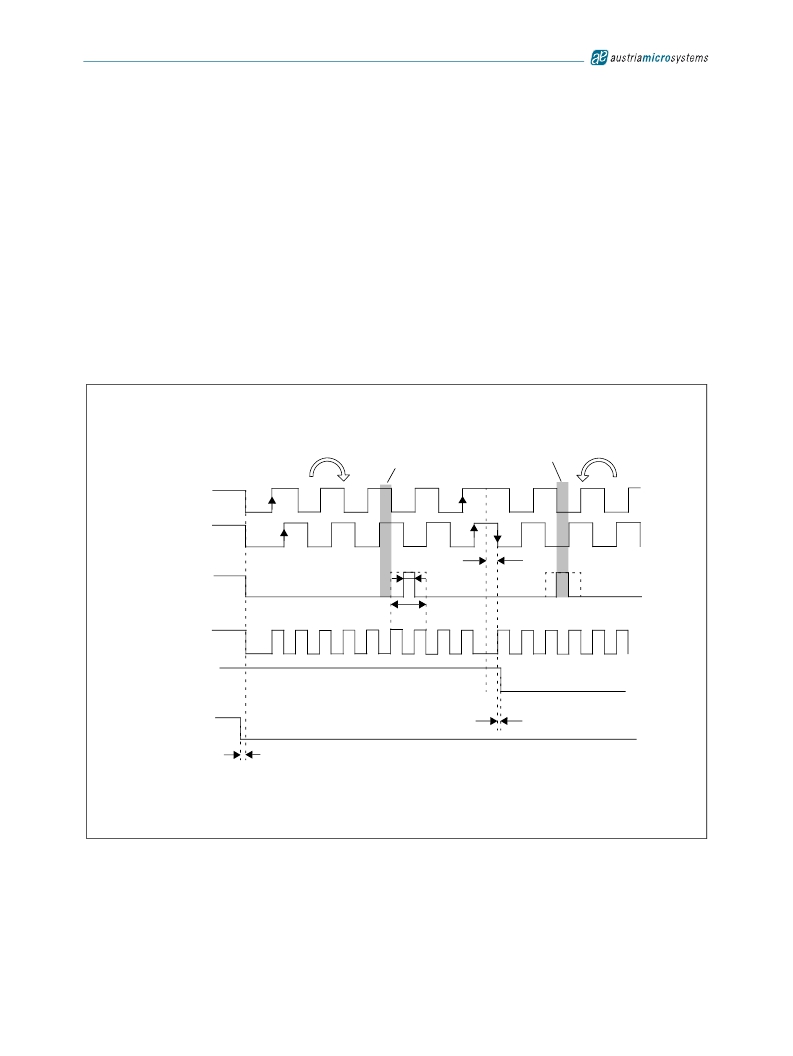

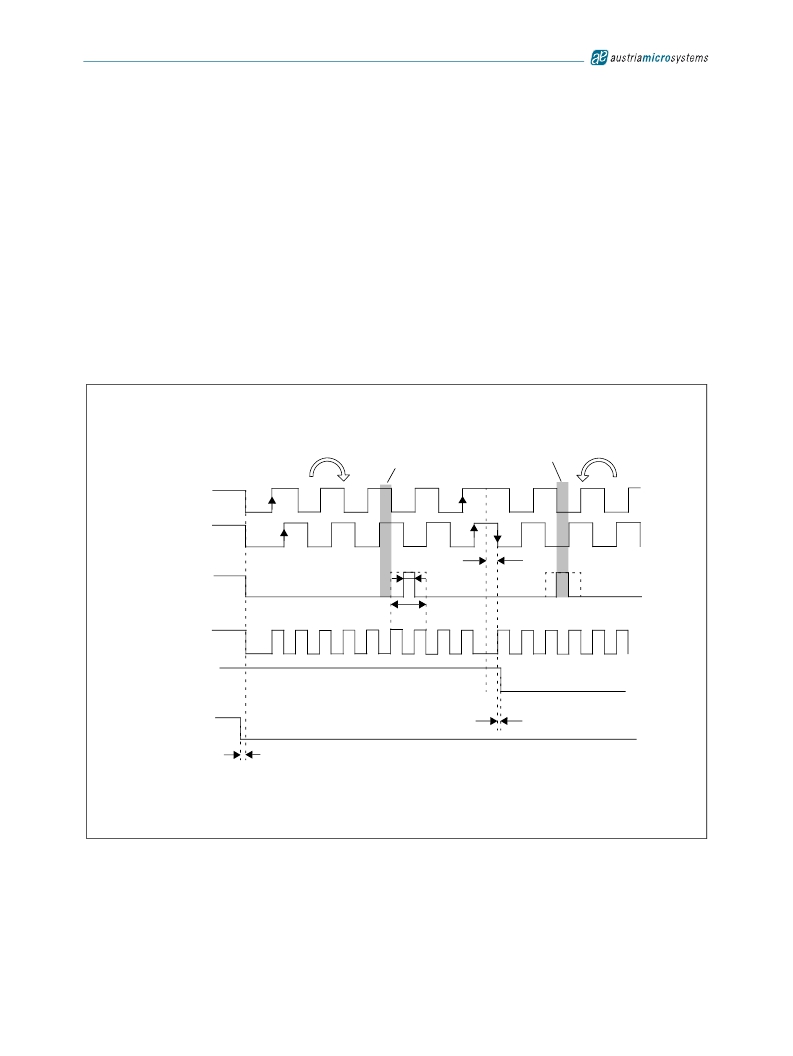

�Three� different� incremental� output� modes� are� possible� with� quadrature� A/B� being� the� default� mode.� Figure� 8� shows� the� two-channel� quadrature�

�as� well� as� the� step� /� direction� incremental� signal� (LSB)� and� the� direction� bit� in� clockwise� (CW)� and� counter-clockwise� (CCW)� direction.�

�7.2.1�

�Quadrature� A/B� Output� (Quad� A/B� Mode)�

�The� phase� shift� between� channel� A� and� B� indicates� the� direction� of� the� magnet� movement.� Channel� A� leads� channel� B� at� a� clockwise� rotation� of�

�the� magnet� (top� view)� by� 90� electrical� degrees.� Channel� B� leads� channel� A� at� a� counter-clockwise� rotation.�

�Figure� 8.� Incremental� Output� Modes�

�Quad� A/B-Mode�

�Mechanical�

�Zero� Position�

�Rotation� Direction�

�Change�

�Mechanical�

�Zero� Position�

�A�

�B�

�7.2.2�

�Index�

�Step� /� Dir-Mode�

�LSB�

�Dir�

�CSn�

�t� Incremental� outputs� valid�

�LSB� Output� (Step/Direction� Mode)�

�Clockwise� cw�

�Index=0�

�1� LSB�

�Index=1�

�3� LSB�

�Hyst=�

�2LSB�

�t� Dir� valid�

�Counterclockwise� ccw�

�Output� LSB� reflects� the� LSB� (least� significant� bit)� of� the� programmed� incremental� resolution� (OTP� Register� Bit� Div0,� Div1).� Output� Dir� provides�

�information� about� the� rotational� direction� of� the� magnet,� which� may� be� placed� above� or� below� the� device� (1=clockwise;� 0=counter� clockwise;� top�

�view).� Dir� is� updated� with� every� LSB� change.� In� both� modes� (quad� A/B,� step/direction),� the� resolution� and� the� index� output� are� user�

�programmable.� The� index� pulse� indicates� the� zero� position� and� is� by� default� one� angular� step� (1LSB)� wide.� However,� it� can� be� set� to� three� LSBs�

�by� programming� the� Index-bit� of� the� OTP� register� accordingly� (see� Table� 20)� .�

�www.austriamicrosystems.com/AS5140H�

�Revision� 1.4�

�15� -� 37�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ASDMB-ADAPTER-KIT

ASDMB MEMSPEED P II OSC KIT

ASFLMPLP-ADAPTER-KIT

ASFLMPLP MEMSPEED P II OSC KIT

AT24C01-10SI-1.8

IC EEPROM 1KBIT 400KHZ 8SOIC

AT24C01B-TSU-T

IC EEPROM 1KBIT 1MHZ SOT23-5

AT24C02C-XHM-B

IC EEPROM 2KBIT 1MHZ 8TSSOP

AT24C04AN-10SI-2.7

IC EEPROM 4KBIT 400KHZ 8SOIC

AT24C08B-PU

IC EEPROM 8KBIT 1MHZ 8DIP

AT24C1024B-TH25-B

IC EEPROM 1MBIT 1MHZ 8TSSOP

相关代理商/技术参数

AS51400FLF

制造商:TT Electronics / IRC 功能描述:AS51400FLF

AS51400HLF

制造商:TT Electronics / IRC 功能描述:AS51400HLF

AS51400JLF

制造商:TT Electronics / IRC 功能描述:AS51400JLF

AS51401FLF

制造商:TT Electronics / IRC 功能描述:AS51401FLF

AS51401HLF

制造商:TT Electronics / IRC 功能描述:AS51401HLF

AS51401JLF

制造商:TT Electronics / IRC 功能描述:AS51401JLF

AS51402FLF

制造商:TT Electronics / IRC 功能描述:AS51402FLF

AS51402HLF

制造商:TT Electronics / IRC 功能描述:AS51402HLF